Samsung a de grandes ambitions pour le futur de son service de production de semi-conducteurs. Selon son plan quinquennal, le géant coréen ambitionne de tripler son chiffre d’affaires dans le secteur à l’horizon 2027. Avec une « arme fatale », cette année-là, Samsung ambitionne de produire des transistors mesurant seulement 1,4 nanomètre.

Pour l’heure, Samsung est, avec TSMC, la seule « fonderie » à utiliser de manière industrielle la gravure en ultraviolets extrêmes. Mais le chaebol (conglomérat) reste loin derrière TSMC tant en parts de marché (TSMC produit entre 90% et 95% des puces en dessous de 7 nm !) qu’en maîtrise du procédé. C’est l’avance technologique de TSMC qui a poussé Qualcomm à passer de Samsung (qui gravait le Snapdragon 8 Gen 1) au Taïwanais pour sa version « Plus ». C’est elle aussi qui aussi poussé Nvidia à préférer le 4 nm de TSMC pour ses GeForce RTX 4000 (les RTX 3000 étaient gravées en 8 nm par Samsung).

Dépassé par TSMC, Samsung entend ne pas le rester. Selon Bloomberg, le Coréen aurait investi trois fois plus de ressources sur sa technologie 3 nm que pour les « nodes » (les autres paliers de finesse de gravure, comme le 8 nm, le 4 nm, etc.) précédents. Si Samsung est le roi de la méthode Coué par rapport à TSMC qui est un grand taiseux, le Coréen semble cependant faire confiance à sa prochaine technologique de gravure.

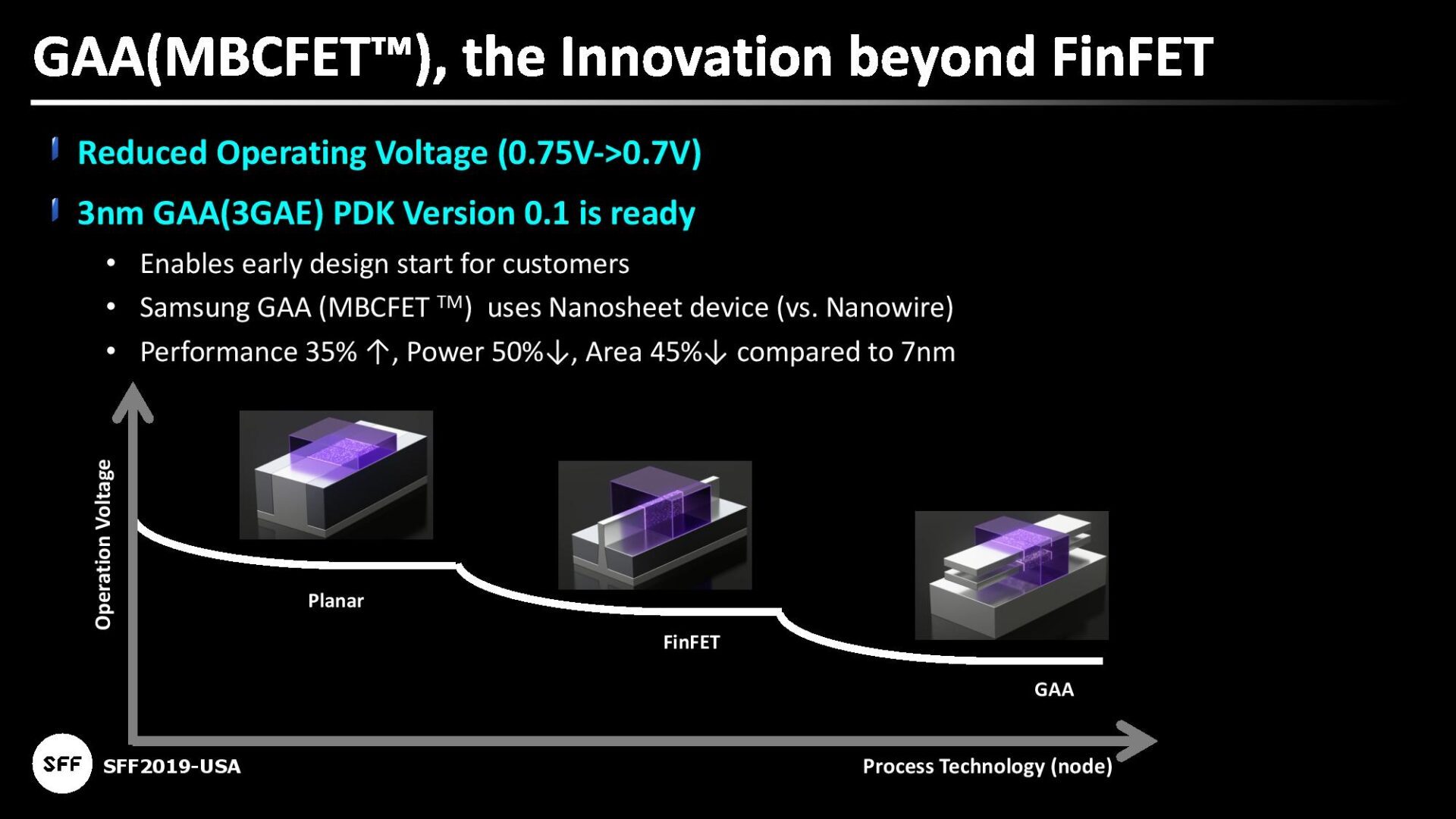

Elle a un avantage sur celle actuellement utilisée par TSMC. Le 3 nm sera la première génération de transistors au monde à se passer de la structure FinFET en vigueur depuis une décennie au profit de la technologie « Gate all-around » ou GAAFET. Samsung n’a pas son exclusivité : TSMC et Intel devrait déployer cette technologie dès le 2 nm entre 2024 et 2025 (la technologie s’appelle RibbonFET/nanoribbon chez Intel et MBCFET chez Samsung).

Samsung prévoit une feuille de route aussi agressive que celle de ses concurrents en matière de réduction de la taille des composants : le 3 nm est prévu pour 2024 et le 2 nm, qui sera un raffinement du précédent procédé, serait industrialisé dès 2025. Avec une descente à 1,4 nm en 2027.

À l’image d’Intel qui se place en « champion occidental des semi-conducteurs », Samsung joue aussi la carte de la diversification des sites de production avec une usine actuellement en construction à Taylor, dans les alentours d’Austin (Texas). Un important site industriel à 17 milliards de dollars !

Après s’être battus sur des centaines, puis des dizaines, puis quelques nanomètres, le futur de la réduction de la taille des transistors va donc se jouer, dès 2024, sur des dixièmes de milliardièmes de mètre. Avant de se heurter à un mur ?

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.

Source : Bloomberg