L’année 2023 ne sera pas celle de la gravure de masse en 3 nm. Si la puce A17 des futurs iPhone 15 Pro est sans doute déjà en pré-production dans les très secrètes usines de TSMC, ce devrait être l’exception qui confirme la règle. Si Apple a des poches immensément profondes et un petit portfolio de puces, des acteurs comme Qualcomm et MediaTek devraient attendre un peu plus longtemps avant de faire le grand saut.

Lire aussi : TSMC toujours plus fort : le 3 nm à l’heure et une usine à 35 milliards de dollars (mars 2021)

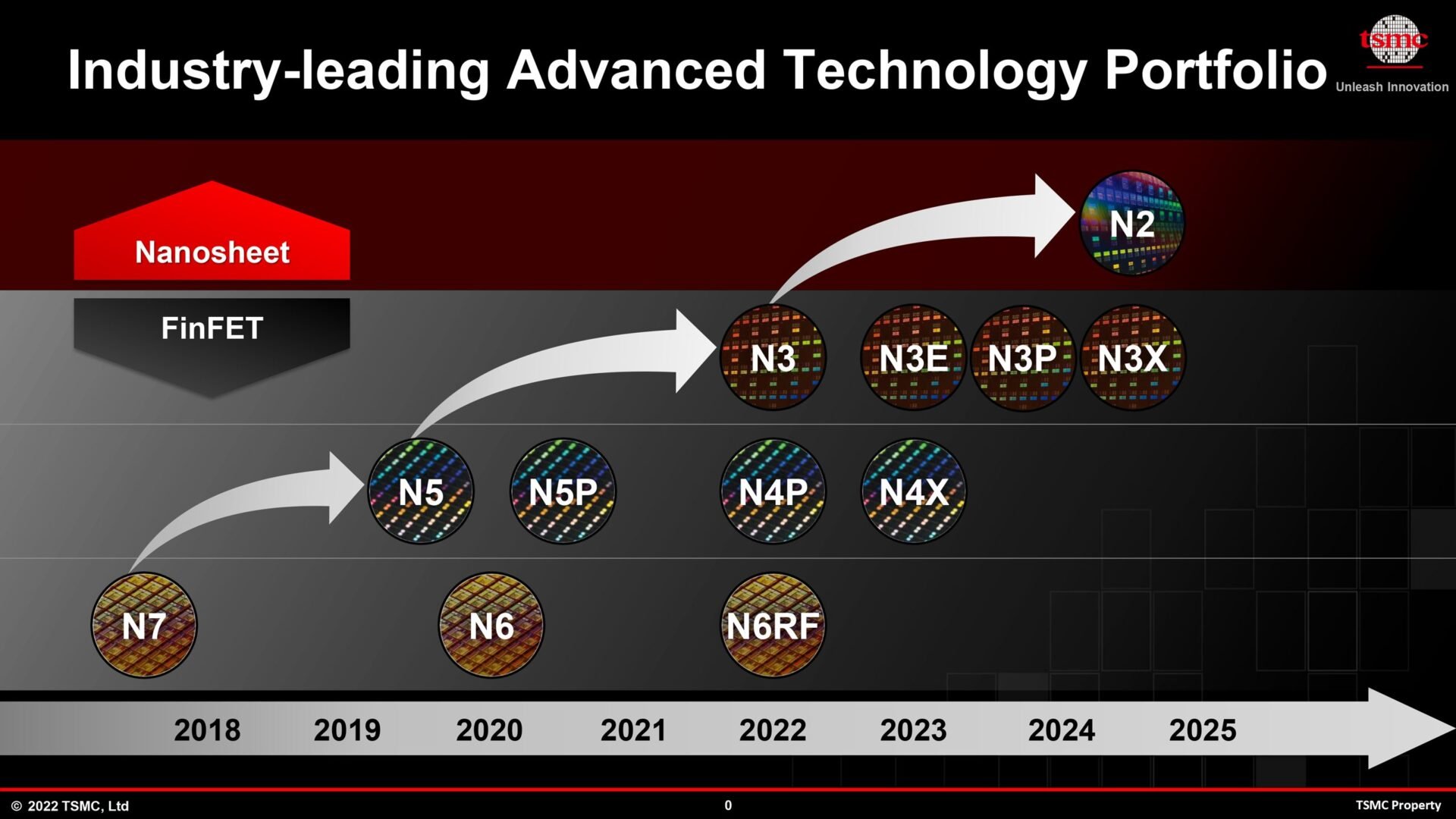

Il faut dire que les procédés 3 nm – un pluriel d’importance – ne sont pas des « nodes » (le jargon pour parler des finesses de gravure) anodins. Que ce soit chez Samsung, où ce node repose sur une nouvelle génération de transistors. Ou chez le champion TSMC, où le procédé N3 reste sur des transistors FinFET, mais où toute la production est repensée… et où les prix explosent et les rendements baissent.

Plusieurs procédés 3 nm

Outre le fait qu’il n’existe pas de norme internationale pour qualifier les nodes de production (chacun compte ses nanomètres dans son coin), les procédés sont différents dans l’approche. Pour TSMC, là où le 6 nm était l’extension du 7 nm et le 4 nm celle du 5 nm, le 3 nm est bien une étape majeure. Qui nécessite que les puces qui doivent être gravées dans ce node, soit, dès le départ, conçue pour cela.

A lire aussi : Jusqu’où ira la miniaturisation des puces ? Samsung promet des transistors de 1,4 nm en 2027 (oct 2022)

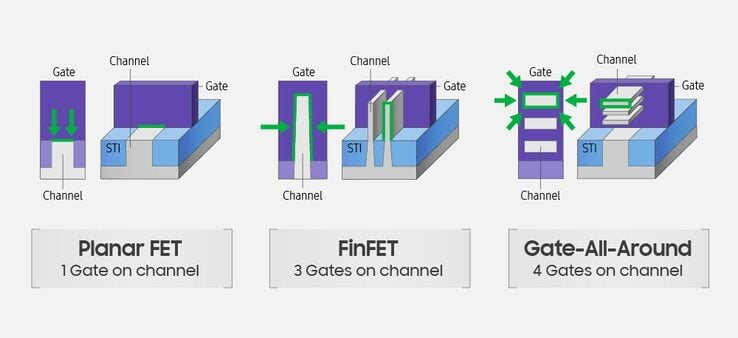

Plus restrictif encore est le 3 nm de Samsung. Alors que Coréen s’est enorgueilli d’avoir été le premier sur cette finesse de conception des circuits, Samsung a aussi précisé que ce node serait le premier à faire appel à la nouvelle génération de transistors dits « Gate All Around » ou GAAFET chez Samsung (Nano-sheet chez TSMC et Nanoribbon chez Intel). Succédant au FinFET en service depuis plus d’une décennie, ces nouveaux transistors nécessitent un travail bien plus profond en matière de conception.

Les deux méthodes de fabrication de TSMC et Samsung ayant ceci en commun qu’ils utilisent massivement les fameuses machines de lithographies à ultraviolets extrêmes (EUV). Ces machines hors de prix (aux alentours de 150 millions d’euros la pièce !) sont celles qui ont réussi à faire passer le monde des semi-conducteurs en dessous de 8 nm. Utilisées pour quelques étapes à partir de 7 nm en complément des machines DUV (deep ultraviolets) classiques, leur usage est bien plus intensif à mesure que la finesse de gravure se réduit.

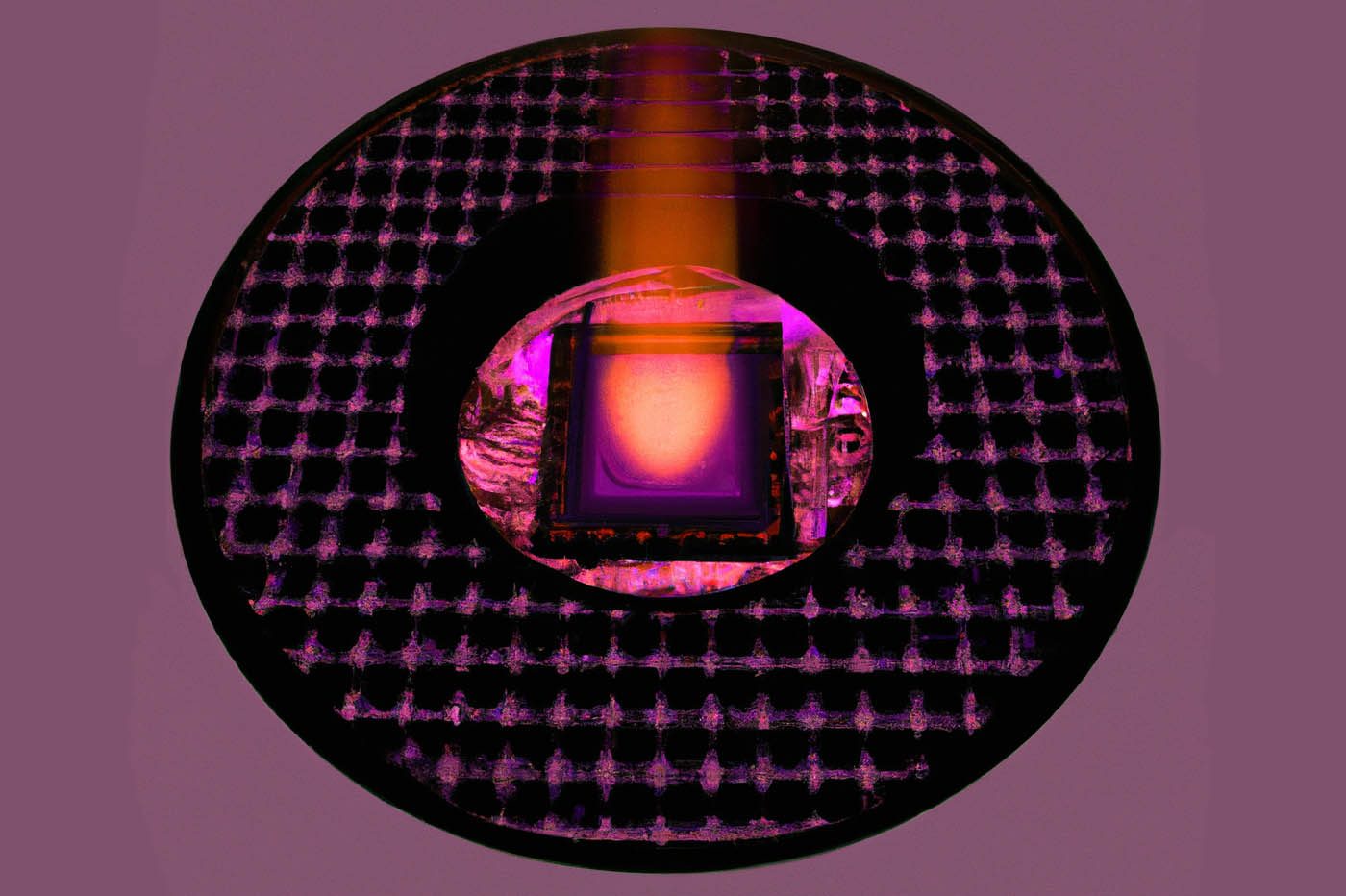

Si d’un côté, elles limitent le nombre de passages de la galette de silicium qui peut conduire à des économies (moins d’étapes = moins d’erreurs = meilleurs rendements), le fait qu’elles soient désormais utilisées à toutes les étapes de production de la puce fait gonfler le prix des wafers (le temps d’usage de chaque machine influe sur le prix final). Les wafers sont les fameuses “galettes” de silicium sur lesquelles les circuits des futures puces sont gravés.

Inflation des prix

Mesurant 300 mm de diamètre, le wafer dit « 12 pouces » introduit en 2001/2022 est le support des puces les plus modernes – il existe toujours des lignes de production en 150 mm (6 pouces) et 200 mm (8 pouces) pour les puces les moins coûteuses. Si la galette de silicium a un prix fixe en tant que support vierge, son prix varie énormément selon le procédé de gravure employé pour « écrire » les composants à sa surface. Et le node 3 nm a repoussé les prix encore plus haut que par le passé, avec un tarif estimé de 20 000 dollars par wafer.

A lire aussi : TSMC : l’usine de gravure en 3 nm sera opérationnelle au second semestre 2022 (nov. 2020)

Si on compare au 5 nm à 16 000 $ et au 10 000 $ du 7 nm, le prix fait mal. Ce d’autant plus que les 60% de coût supplémentaire entre le 5 nm et le 7 nm permettaient tout de même de graver jusqu’à 80% de puces (du même nombre de transistors) en plus. Alors que le passage du 4/5 nm (même procédé) vers le 3 nm ne permet qu’une augmentation du nombre de transistors de seulement 30%. La faute au fait que toutes les parties des puces ne peuvent pas profiter également de la réduction de la taille des circuits – on réduit plus facilement les cœurs CPU que la mémoire SRAM intégrée.

Ce plus, l’inflation des tarifs des wafers n’est pas la seule à faire mal. Le changement de node, voire le changement de structure des transistors (Samsung GAAFET et son équivalent Nanosheet chez TSMC) implique d’autres dépenses. Notamment celles des logiciels de conception de semi-conducteurs de chez Cadence et Synopsys. Loin d’être anecdotiques, ces outils incontournables pour la production de puces sont une des raisons (avec le blocage des machines EUV du néerlandais ASML) pour lesquelles la Chine ne peut pas produire de processeurs de pointe.

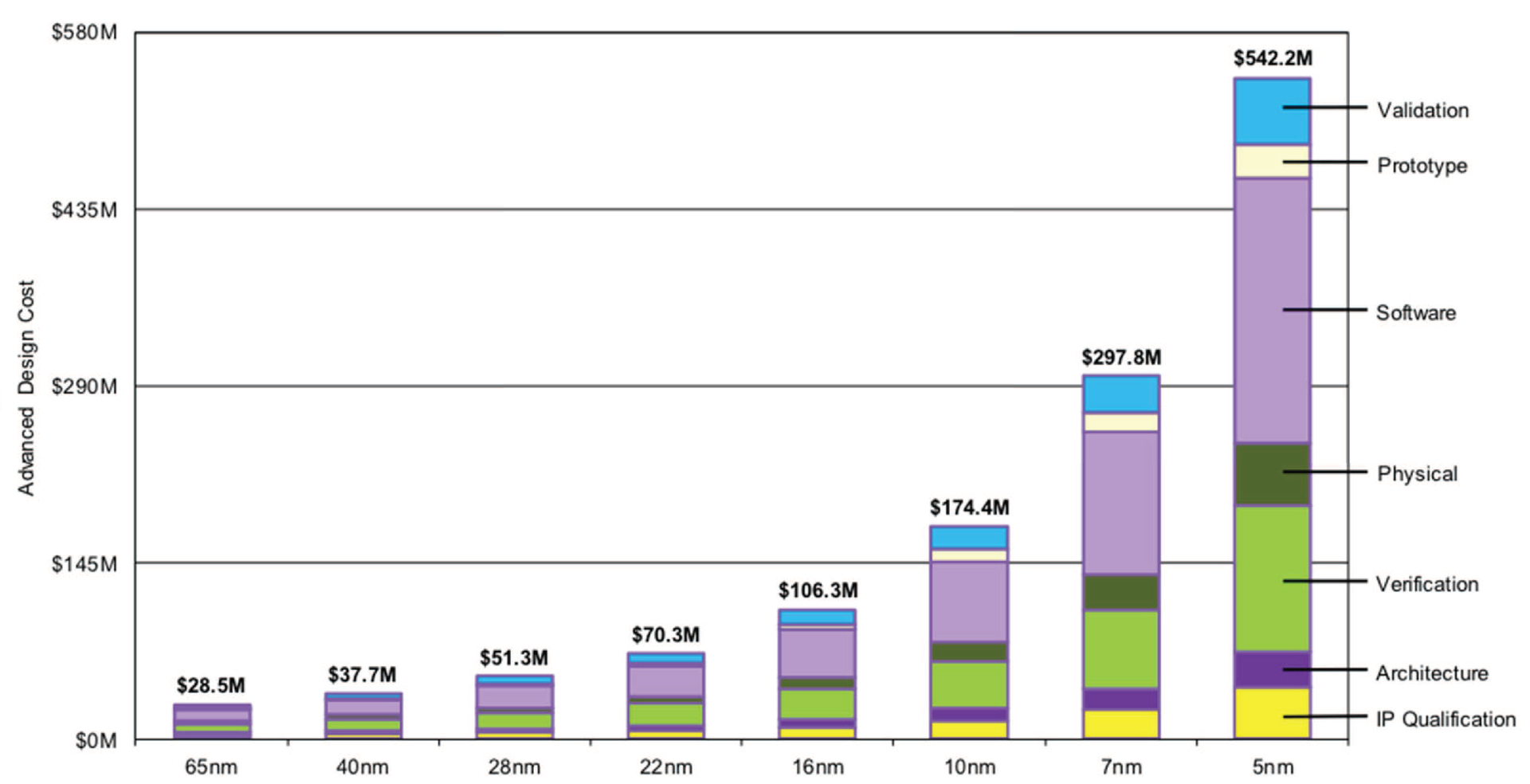

Il suffit de voir l’inflation du coût de la conception des puces : avant même d’avoir appuyé sur le bouton « start » de la production industrielle, le design d’une puce de 5 nm a pu coûter un demi-milliard d’euros ! Et ça risque d’être encore pire pour le 3 nm GAAFET… Ce qui ne veut pas dire que la production va être impossible. Car si le déploiement pourrait être ralenti, les industriels sont au pied du mur.

Une guerre des prix en vue ?

Dans le monde des procédés de fabrication de pointe, TSMC a l’avantage sur Samsung. C’est en effet le Taïwanais qui produit 90% des puces gravées à 7 nm ou moins. Une position ultra-dominante qui pousser le Coréen à constamment jouer la carte du prix pour attirer des clients. Mais alors que TSMC était en position de force pendant la période de pénurie pour maintenir des prix élevés, le vent pourrait tourner. Car avec le peu de gain de densité qu’apporte le 3 nm (appelé N3) par rapport au 5 nm, les 20 000 $ par wafer ne seraient intéressants qu’en cas de puces à très (très !) haute valeur ajoutée. Selon des analystes interrogés par nos confrères de fudzilla, ce coût élevé inciterait les concepteurs de puces que vous connaissez – AMD, Qualcomm, MediaTek, etc. – à attendre et se concentrer sur les nodes 4 et 5 nm. Laissant le champ libre à Apple pour payer à prix d’or le 3 nm pour ses puces.

Seulement voilà, si Apple est un client important à très haut volume (et haute valeur ajoutée), il ne suffira pas à faire tourner les usines à plein régime. Or, les usines sont là, les investissements ont été faits. Et le seul moyen de rentabiliser les dizaines de milliards investis est de les faire tourner. Voilà pourquoi, toujours selon les analystes, TSMC pourrait rogner sa marge et faire baisser ses prix pour attirer le chaland. Ce qui aura pour répercussion de mettre la pression à Samsung, challenger dans le domaine, pour qu’il pratique les prix les plus bas possibles.

À lire aussi : IBM et Samsung ont développé les transistors du futur (Déc. 2021)

On en conclut dont que si l’industrie traîne un peu les pieds pour le lancement du 3 nm, qui devrait être l’exclusivité d’Apple dans un premier temps, la pression sur TSMC et Samsung de rentabiliser leurs investissements colossaux devrait les pousser à faire baisser les prix au plus vite. Mais ce ralentissement organique pourrait peser sur le futur de la conception des puces. Avec une feuille de route publique qui s’arrête à 2 nm chez TSMC (1,8 nm chez Intel pour son node Intel 18) et le passage des wafers de 300 mm à 450 mm toujours reporté aux calendes grecques, la « friction » que cause actuellement le node 3 nm pourrait ralentir, un temps, l’industrie dans ses développements. Une industrie qui est, dans certains domaines comme la mémoire, en pleine surchauffe.

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.