« La plus grosse évolution du x86 depuis dix ans » : ce sont les mots très vendeurs des équipes d’Intel lors de la présentation technique de la prochaine et douzième génération de processeurs « Core » lors de leur Architecture Day. Une belle promesse qu’il va falloir tenir face à un monde des puces en pleine ébullition, et à un AMD très en forme… et surtout très performant. Dans les limbes, il y a à peine 5 ans, AMD est revenu sur le devant de la scène avec son architecture Zen dans les processeurs, puis dans les GPU avec RDNA. Empêtré dans des retards et des soucis de gouvernance, Intel n’a pas sur endiguer la remontée d’AMD et a même perdu plusieurs courses à la puissance.

Lire aussi : Intel annonce Arc, son premier GPU dédié aux gamers

Mais depuis la période de transition de l’ancien patron Bob Swan, qui a remis les comptes et quelques priorités à jour, et surtout avec l’arrivée de la rock star des puces, Pat Gelsinger, Intel est en pleine frénésie d’annonces. Dans le torrent de nouveautés, de feuilles de routes, de performances, etc. il a dévoilé les détails des futures puces Core 12e gen, nom de code « Alder Lake ». Des processeurs que nous allons retrouver aussi bien dans les petits PC embarqués que dans les grosses tours gaming. Et qui fonctionnent selon un mode inédit dans le monde du x86.

Deux types de cœurs façon big.LITTLE

Dans votre main ou dans votre poche, vous avez un appareil dont le processeur est de type « big.LITTLE ». Tous les SoC ou presque intégrés dans les smartphones sont organisés de la même façon : ils sont équipés de quelques « cœurs » CPU à haute puissance pour lancer les applications et effectuer rapidement les tâches difficiles (gaming, retouche d’image, etc.). À leur côté se trouvent des cœurs basse puissance qui s’occupent des opérations moins intenses et exécutent les applications en tâche de fond. C’est cette structure, appelée big.LITTLE, qui permet à nos terminaux de tenir la journée, les cœurs de basse puissance évitant que la batterie ne soit consommée par un gros cœurs certes performants, mais énergétiquement bien moins efficaces.

Si Intel l’a déjà testée par le passé dans un produit assez confidentiel – la puce ultramobile Lakefield –et avec très peu de succès, c’est la première fois de son histoire qu’il décline cette organisation de puce à une génération entière de composants. Mais, conscient des limites de Lakefield et de l’absence de pilotage de l’ensemble, Intel a développé toute une panoplie de nouveaux composants logiques.

Efficient Core : au secours de l’endurance

Petits, mais costauds : c’est ainsi qu’Intel a présenté son Efficient Core (E-Core), son cœur le plus efficace. Dans une puce comme Lakefield, ces petits cœurs étaient des Atom bien souffreteux. Dans Alder Lake, il s’agit de toute nouveaux cœurs appelés Gracemont, dont le niveau d’efficacité est d’une toute autre magnitude. Tant est si bien que ce n’est pas avec les Atom qu’Intel les compare, mais avec son architecture de cœurs haute puissance Skylake, qui a longtemps fait le succès d’Intel.

De manière étonnante, le nouvel « Efficient Core » est plus performant que Skylake, aussi bien en simple qu’en multitâche, en consommation énergique comme en puissance. En simple tâche, il est déjà plus de 40% plus performant à consommation énergétique égale et consomme 40% de moins d’énergie à performances égales.

Mais c’est en multicœurs que ces cœurs CPU brille vraiment, poussant les performances à +80% à conso égale et la consommation à -80% par rapport au même niveau de performances. Et c’est sans même parler du gain d’espace : 4 cœurs « Gracemont » prennent la même place sur la puce qu’un seul cœur Skylake.

Performance Core : toujours plus vite

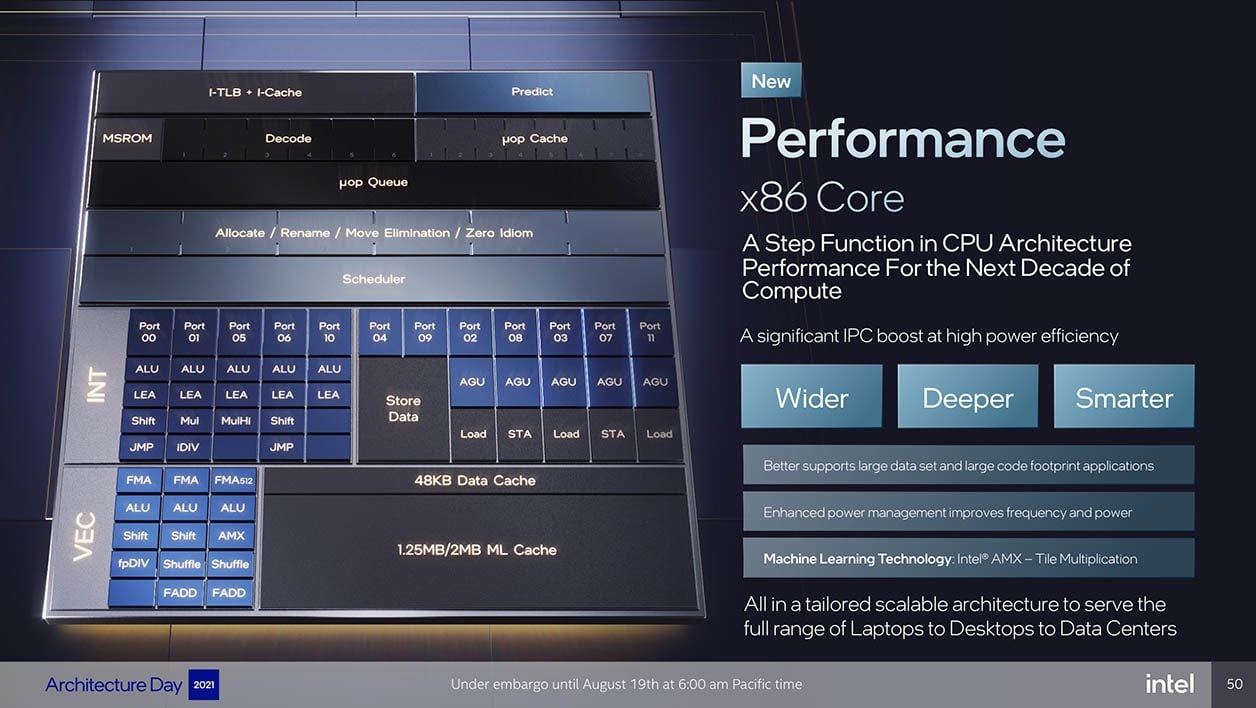

Le nouveau cœur hautes performances (P-Core) d’Intel a pour nom de code « Golden Cove ». Un cœur unique qui succède à trois cœurs spécialisés (Sunny Cove pour les serveurs, Willow Cove pour les PC portables et Cypress Cove pour les tours). Un « Monsieur Plus » des cœurs x86 dont les promesses sonnent comme une chanson de Daft Punk : Wider, Deeper, Smarter (à vos samplers).

Sans rentrer dans des détails ultra-complexes qu’Intel a communiqués, il faut retenir que ces cœurs hautes performances disposent de plus… de tout ! Qu’il s’agisse de mémoire cache, d’unités de calcul, de profondeur de bits traités, etc. Toute la puce est revue en profondeur et ses unités sont agencées de manière à être plus efficaces. Le tout est épaulé par une toute nouvelle unité de gestion de l’alimentation et un nouveau coprocesseur vectoriel très utile dans les calculs de type IA (apprentissage machine notamment).

La question à trois ngultrum (la monnaie du Bhoutan) est évidemment : comment faire fonctionner de concert les E-Core et les P-Core de manière efficace ? Si cela ne pose aucun souci dans le monde des smartphones, le monde de l’informatique « Windows + x86 » et les déboires de Lakefield ont déjà douché quelques espoirs. Cela, Intel en était bien conscient et les ingénieurs ont donc développé un nouveau composant en charge de la bonne conduite de cet orchestre de cœurs.

Thread Director : le chef d’orchestre des tâches

L’un des éléments, trop souvent oublié, du succès énergétique de la puce M1 d’Apple est sa capacité à analyser intelligemment la difficulté des tâches qu’elle a à traiter. Si la tâche est importante, elle va sur les cœurs hautes performances, mais dès qu’elle n’est plus critique, elle sera déplacée sur les cœurs basse consommation.

C’est exactement ce qu’Intel a fait de manière matérielle dans Alder Lake en développant une toute nouvelle unité appelée « Thread Director ». Puce dans la puce, le « directeur des taches » est un véritable chef d’orchestre qui dit qui fait quoi et quand. Loin de s’appuyer sur de bêtes scénarios fixes, il gère de manière dynamique l’attribution des tâches, sait quand déplacer telle tâche sur le bon type de cœur, etc. Et surtout, il le fait vite : là où un planificateur des tâches logiciel prend des décisions en quelques centaines de millisecondes, Intel clame que son Thread Director peut prendre une décision en à peine 30 microsecondes.

Mieux : il peut s’adapter à n’importe quel type de tâche en travaillant de concert avec le système d’exploitation, parfois le seul à même de savoir ce dont l’utilisateur a besoin. Le premier à profiter de cette communication très fine sera Microsoft. Selon un intervenant de chez l’entreprise de Redmond, le futur Edge et quelques éléments de Windows 11 tireront pleinement parti de du Thread Director.

Lire aussi : Windows 11, l’ISO de la Preview est disponible au téléchargement, voici comment l’installer

À notre connaissance, ce sera la première fois qu’un OS saura exactement quel type de cœur traite tel type de tâche. Jusqu’à présent, le programmateur (scheduler) n’avait aucune visibilité du type de tâche qui était exécutée sur un thread. Copie de la mémoire, boucle ou calcul, il lui était impossible de savoir et impossible de prédire de manière aussi fine.

Il reste cependant à voir non seulement à quelle vitesse ce chef d’orchestre sera pris en charge par les futurs systèmes d’exploitation. Ainsi que son impact réel sur les performances et la consommation énergétique dans une puce x86.

Jeu de brique et gravure « Intel 7 »

Comme son nom l’indique, l’Architecture Day n’est pas le Marketing Day : Intel n’a dévoilé aucun produit, aucune composition, aucune fréquence finale de ses futures puces. Le géant s’est pour l’heure contenté de présenter la fourchette de fonctionnement énergétique de sa nouvelle génération, allant de 7W à 125W, soit à peu près tous les types d’ordinateurs grand public comme professionnels (hors serveurs et calculateurs).

Mais on sait qu’Intel va jouer à un jeu de briques pour composer ses futurs produits. Le concepteur de puces a présenté un éclaté de ses technologies – des « IP » dans le jargon, détaillant les différents composants logiques comme les types de cœurs (P-Cores, E-Cores), les configuration GPU (Xe en 32 ou 96 unités d’exécutions), les équipements (gestion des écrans, du Thunderbolt, etc.) ou encore les types de mémoire.

Dans sa configuration maximale, Alder Lake sera un SoC de 8 P-Core (capables de gérer deux tâches chacun) et 8 E-Core (une tâche par cœur) affichant donc un total de 16 cœurs et 24 tâches simultanées. Les contrôleurs mémoire pourront aller de la mémoire basse consommation LPDDR 4x à de la grosse DDR5-4800. Un nouveau contrôleur PCIe de 5e génération fait son apparition ainsi qu’une mémoire d’interconnexion (Compute Fabric) capable de gérer un flot de données internes de 1To/s !

À découvrir aussi en vidéo :

Autre détail d’importance, ce n’est pas TSMC mais bien Intel qui gravera ses puces selon le procédé nouvellement nommé « Intel 7 ». Jadis appelé « 10 nm SuperFin », ce procédé a été nommé ainsi, car bien que la partie la plus fine des transistors soit gravée en 10 nm, la densité réelle en transistors est équivalente, voire dépasse les procédés 7 nm de TSMC. La guerre des composants se joue aussi sur le terrain de la communication !

Point d’attente interminable, comme pour le GPU ARC dont nous vous avons déjà parlé : le portfolio de puces de 12e génération « Alder Lake » sera présenté dans le courant de l’automne 2021. Soit en parfaite synchronisation avec l’avènement de Windows 11. Quel heureux hasard !

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.