Une branche technologique de la marine américaine – US Navy – a passé un contrat avec Intel qui va lui permettre d’accéder à ses usines de dernière génération en Arizona et en Oregon pour produire des puces à technologie « empilée ». La division Crane du Naval Surface Warfare Center, qui dépend de la Navy, a en effet besoin d’avoir accès à un outil de production sûr qui lui permette de fabriquer des puces à la fois à la pointe de la technologie sans mettre à genoux son budget. Dans le mot « sûr », il faut comprendre ici des usines « amies » où ni les Chinois ni les Russes ne peuvent mettre les pieds.

L’épisode de guerre technologique entre les USA et la Chine au travers du dossier « Trump contre Huawei » a sans doute favorisé la branche gouvernementale d’Intel (Intel Federal LLC) face à Samsung et TSMC. Deux entreprises de pays certes alliés, mais dont les « fabs » sont en Asie (même si TSMC disposera bientôt d’une usine de pointe aux USA) et donc plus facilement infiltrables par des agents espions. Le nom du projet de la Navy ? Le bien nommé « S.H.I.P », pour « State-of-the-Art Heterogeneous Integration Prototype » (Prototype d’intégration hétérogène à pointe de la technologie). Ça bosse dur au département de dénomination de la Navy…

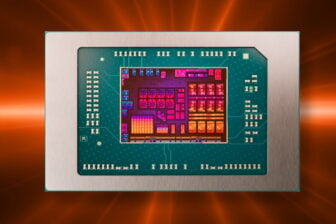

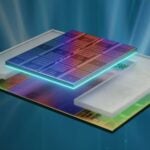

Quand bien même Intel est en retard pour sa technologie 7 nm (sans même parler du 5 nm), son process 10 nm offre des résultats assez proches du 7 nm en termes d’espacement réel des composants. Ce qui en fait un procédé de pointe. Surtout, Intel maîtrise très bien l’empilement de « morceaux » de puces, produits à des finesses de gravure différente au travers de ses technologies appelées EMIB, Foveros ou Co-EMIB (EMIB + Foveros). L’intérêt d’empiler des blocs de processeurs ? Cela permet de faire drastiquement baisser le coût final des puces. Un élément encore plus critique dans le cas de puces militaires produites, au mieux, à quelques milliers d’exemplaires, contre des millions voire des milliards pour les processeurs et autres SoC grand public.

Couper et assembler des éléments de processeurs permet de profiter d’un meilleur rendement, mais cela permet aussi de créer des puces « à la carte » plus compactes. En intégrant, par exemple, la mémoire directement au-dessus des processeurs, comme le fait Intel avec Lakefield. Voire en superposant carrément plusieurs types de puces.

Aucun détail n’a évidemment filtré quant à la nature des composants qui seront produits, mais la Navy a fait savoir qu’elle compte profiter des technologies EMIB et Foveros pour intégrer ses propres puces à des « briques » Intel déjà existantes.

Source : Intel

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.