Au-delà de Rubin

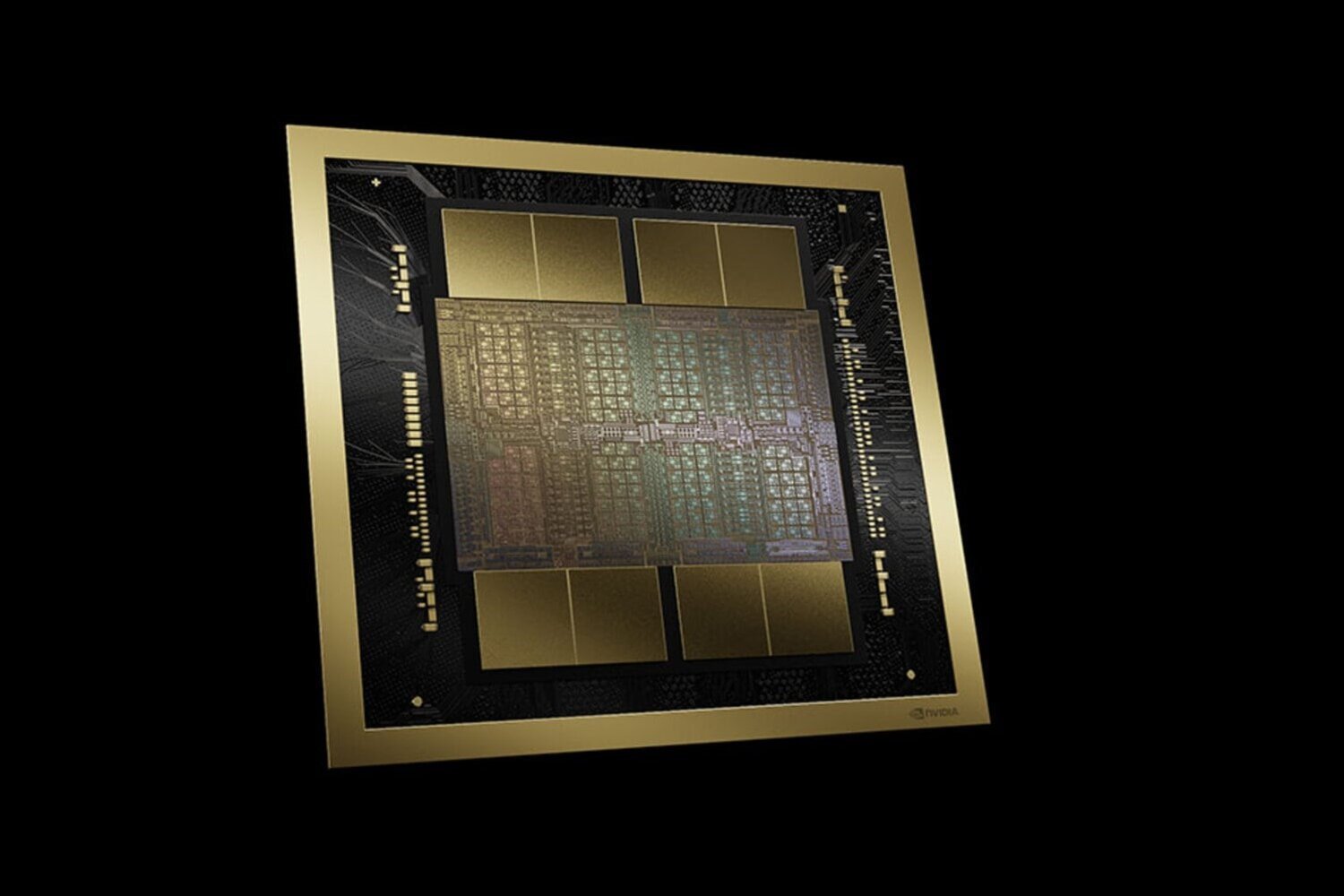

Les solutions actuelles de NVIDIA, à commencer par les H100 et H200 (architecture Hopper), ou les plus récents B100 et B200 (architecture Blackwell), permettent à la société de profiter pleinement de l’engouement autour de l’IA. L’avenir s’annonce aussi radieux pour l’entreprise ; nous avons appris il y a peu que la prochaine génération de puces consacrée à l’intelligence artificielle, dont le nom de code est Rubin, était susceptible de débarquer dès le milieu de l’année 2025. Projetons-nous encore plus loin dans le futur, avec une conception présentée dans le cadre de l’IEDM 2024.

La vision qu’a NVIDIA des puces du futur repose sur deux approches considérées, à juste titre, comme des leviers indispensables pour dépasser les contraintes techniques actuelles : l’empilement 3D, qui n’est déjà plus une chimère, et la photonique de silicium.

L’esquisse d’une puce IA

La photonique du silicium, abrégée SiPh, pourrait supplanter les interconnexions électriques actuelles. Comme son nom l’explicite, elle repose sur le principe du transfert d’informations basé sur la lumière. Elle doit favoriser une hausse de la bande passante, ainsi qu’une réduction de la latence et de la consommation. Comme le souligne Ian Curtress, pour son accélérateur IA du turfu, NVIDIA envisage le recours à la SiPH à la fois pour la communication intra-puce et inter-puce.

Here’s @NVIDIA‘s vision of the future of AI compute.

Silicon photonics interposer

SiPh intrachip and interchip

12 SiPh connects, 3 per GPU tile

4 GPU tiles per tier

GPU ‘tiers’ (GPU on GPU?!?)

3D Stacked DRAM, 6 per tile, fine-grainedFrom #iedm24. My guess, 2028/2029/2030… pic.twitter.com/5IsDkYSWT2

— 𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 (@IanCutress) December 8, 2024

Pour le reste, le schéma présente une conception à base de tuiles (dans la lignée des dernières générations de Core d’Intel pour prendre un exemple grand public) GPU / DRAM, mais faisant la part belle à l’empilement vertical. Comme un immeuble pour l’habitat, cette approche permet d’augmenter drastiquement la densité sans agrandir la surface. Toutefois, si vous nous autorisez une analogie culinaire, au même titre que pour un croque-monsieur, le morceau de jambon reste bien au chaud entre ses deux tranches de pain de mie, ce packaging 3D pose plusieurs défis relatifs au refroidissement (et à la gestion de l’énergie).

À ce stade, en particulier pour le SiPH, les technologies ne sont pas suffisamment maîtrisées pour envisager une production de masse de puces telles que celle décrite ici. Ian Cutress estime ainsi que l’accélérateur croqué ici verrait vraisemblablement le jour d’ici la fin de cette décennie, plus précisément entre 2028 et 2030.

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.