Eternel challenger tant dans les CPU que les GPU, AMD est une entreprise qui a su se maintenir et progresser grâce à des ingénieurs talentueux… et astucieux. On en tient pour preuve la présentation technologique qu’AMD vient de donner à 33e édition de la conférence spécialisée Hot Chips. Intitulée « Les produits AMD conçus avec un packaging 3D », cette conférence donnée par un vétéran de l’assemblage des puces, Raja Swaminathan (ex-Intel, ex-Apple) avait pour ambition de montrer les technologies et plans d’AMD autour de l’assemblage des puces, façon jeux de briques.

Lire aussi : AMD empiler de la mémoire cache sur ses futurs processeurs (et les joueurs vont adorer)

Plutôt que de concevoir ses puces en un seul gros « morceau » (approche dite monolithique), l’américain a développé un réel talent pour assembler ses processeurs grand public comme professionnels à partir de petits « bouts » interconnectés.

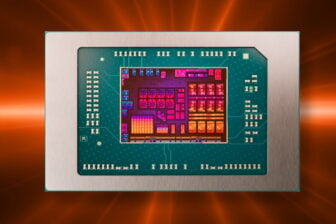

But de l’opération : être capable de monter en puissance en « collant » intelligemment ces morceaux et produire des processeurs moins chers (le rendement des petits composants est toujours supérieur à celui des gros). Les Ryzen et surtout les Threadrippers sont en fait des combinaisons de petits morceaux collés les uns à côté des autres. Mais l’heure est aujourd’hui à l’empilement en 3D.

Un procédé industrialisé dès cette année

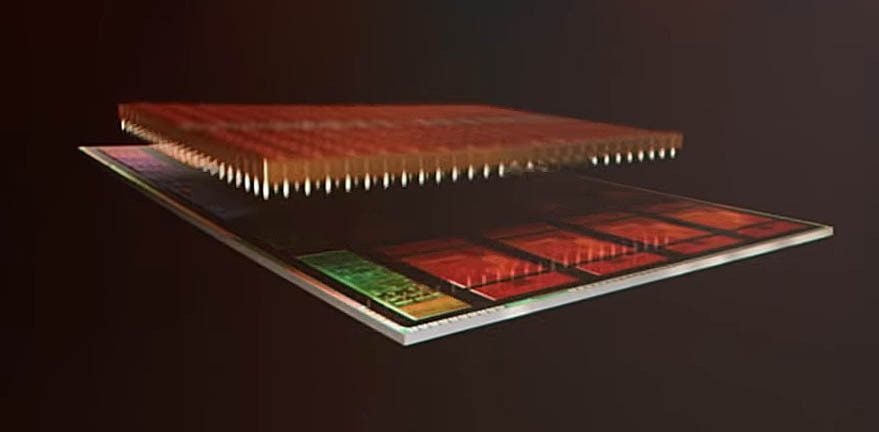

Comme nous vous en avions parlé en juin dernier, AMD a déjà présenté un processeur « normal » avec de la RAM collée dessus. On sait maintenant comment les ingénieurs s’y sont pris : plutôt que de « souder » la mémoire avec des petits picots de métal, qui imposent des points de soudure très larges, les ingénieurs ont fait appel à un procédé plus fin.

Bien plus fin, puisque les interconnexions, obtenues – d’abord un collage diélectrique-diélectrique + cuisson, puis procédé de diffusion à l’état solide – ne mesurent que 9 microns de large, contre environ 50 microns pour les « microbumps » classiques. Une densification des interconnexions nécessaires à l’obtention d’une bonne bande passante.

Avec sa technologie Foveros actuelle, Intel est limité à 50 microns. Mais bien que sa future technologie Foveros Direct soit assez proche de celle d’AMD (10 microns), elle sera uniquement disponible à partir de 2023. Or, par comparaison, le procédé d’AMD utiliserait des technologies déjà maîtrisées, s’inscriraient facilement dans un flux de production actuel et serait industrialisé dès la fin de cette année 2021.

Conserver l’avantage et préparer le futur

Selon les premiers tests publiés par AMD en juin dernier, l’ajout de mémoire (64 Mo) qui triple la quantité de mémoire cache (96 Mo) permet de gagner en moyenne 15% de performances. Dans le milieu des processeurs, un tel gain correspond généralement à une belle évolution de microarchitecture, réalisé ici avec un simple « collage ». Une astuce qui permettrait à AMD de maintenir un très bon rapport performances/prix en attendant le passage à son architecture Zen 4 d’ici à l’automne 2022 prochain. De quoi facilement donner du peps à d’éventuel refresh de Zen 3 en attendant. Voire booster Zen 4 dans le cas où la contre-attaque d’Intel soit trop forte.

À découvrir aussi en vidéo :

Cet empilement de morceaux de puces est sans aucun doute le futur de la production de semi-conducteurs, et ce n’est pas Intel avec son Foveros qui dira le contraire. Pourtant, Intel comme AMD (et leurs partenaires) ont de nombreux défis devant eux. Si l’astuce de cet empilement de mémoire est une belle performance, l’opération est réalisée au-dessus de la mémoire cache existante. Or, pour empiler des cœurs CPU/GPU ou d’autres unités de calcul les uns sur les autres, il va falloir ruser côté dissipation thermique ou encore interférences électromagnétiques.

Le futur sera empilé, mais de nombreux procédés restent à inventer.

Source : Tom’s Hardware US

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.