Avec le déclin de la loi de Moore, l’industrie des semi-conducteurs cherche sans arrêt des voies alternatives pour gagner en performance. Actuellement, ce gain est surtout obtenu en multipliant les cœurs de calcul sur la puce. Mais il y a d’autres possibilités, comme l’optimisation de la mémoire cache. Trois chercheurs du MIT viennent justement de présenter « Jenga », une méthode de gestion de la mémoire cache qui permet d’augmenter la vitesse de calcul de 20 à 30 % tout en réduisant la consommation énergétique de 30 à 85 %. Ce qui est considérable.

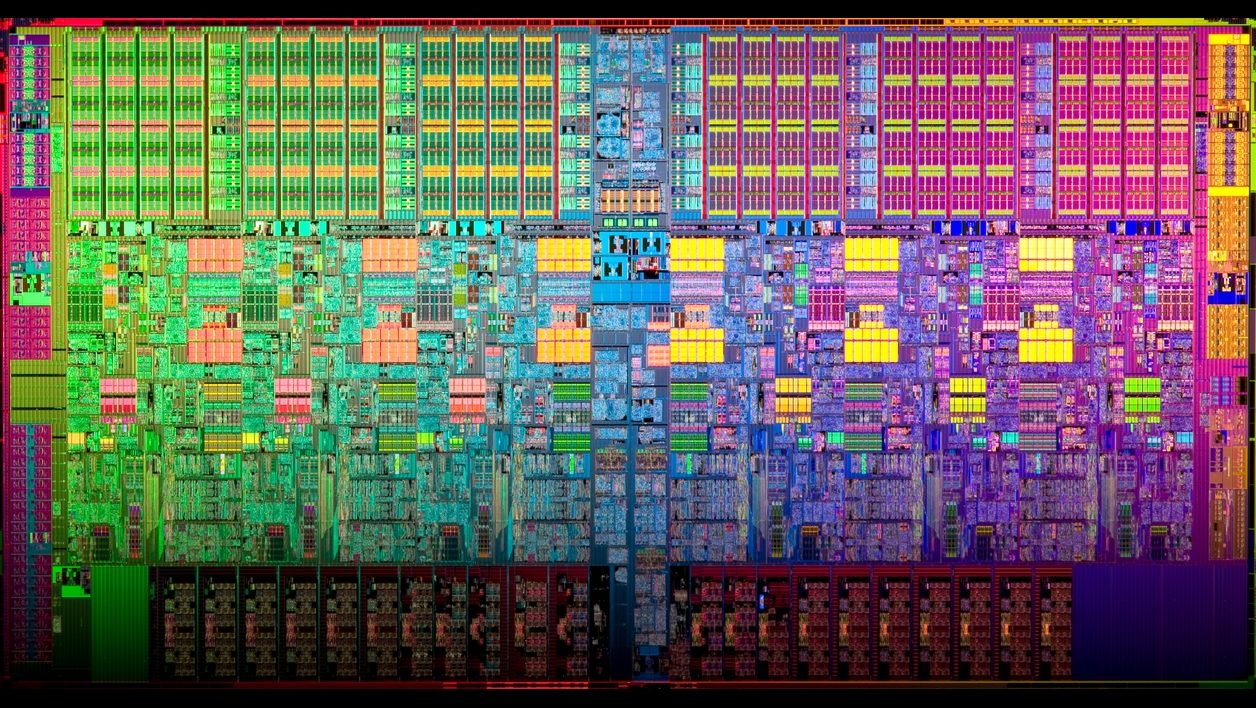

Pour comprendre comment ça marche, un petit rappel s’impose. Dans les processeurs, la mémoire cache est organisée de façon hiérarchique en plusieurs niveaux (L1, L2, L3, L4), du plus rapide et plus petit au plus lent et plus grand. Dans les architectures multicœurs, chaque cœur dispose de caches L1 et L2 qu’il est le seul à pouvoir utiliser. Il dispose également d’un cache L2 à proximité directe qu’il partage avec les autres cœurs. Enfin, L3 est un pool de mémoire partagé situé en dehors de la puce. L1, L2 et L3 sont généralement de la SRAM, L4 plutôt de la DRAM.

Cette hiérarchie est bien pratique, car elle optimise le fonctionnement de la puce en attribuant une priorité d’accès aux données. Celles auxquelles le processeur doit accéder rapidement et en permanence sont stockées en L1 ou L2. Celles qui sont moins importantes viennent en L3 et L4. Mais selon les chercheurs Po-An Tsai, Nathan Beckmann et Daniel Sanchez, la gestion de ces deux derniers niveaux est trop rigide et ne tient pas assez compte des spécificités des applications.

Une structure de données peut, en raison de sa taille, se retrouver répartie sur L3 et L4, ce qui contraint le processeur à systématiquement interroger les deux mémoires pour trouver la donnée recherchée. Il serait peut-être mieux de tout mettre en L4. Certes, le temps d’accès serait plus long, mais il y en aurait moins, et globalement on y gagnerait.

Reconfigurée toutes les 100 millisecondes

L’idée de Jenga est donc de créer des niveaux de cache virtuels à partir des mémoires L3 et L4, et cela en fonction des besoins de chaque application. Parfois, il n’y aurait qu’un niveau virtuel, constitué de L3 ou de L4 ou d’une combinaison des deux. Parfois, il y aurait deux niveaux virtuels, constitué de L3 ou de L4 ou d’une combinaison des deux. Tout est possible, à condition que la performance soit globalement augmentée. L’allocation des ressources est réalisée par un algorithme plutôt complexe qui calcule la configuration optimale de la mémoire toutes les… 100 millisecondes. Une cuisine qui reste totalement transparente pour l’application.

Les chercheurs ont réalisé un prototype de leur technologie en s’appuyant sur une puce avec 36 cœurs, avec un cache L3 SRAM de 512 KO et un cache L3 DRAM de 4 x 256 MO. Ils ont implémenté Jenga sous la forme d’un processus permanent au niveau du système d’exploitation. Ils l’ont ensuite testé sur une vingtaine d’applications. Les résultats sont évidemment très différents. Parfois, Jenga n’apporte rien, mais souvent la performance de la puce s’en trouve améliorée grâce à la réduction du nombre d’accès mémoire. Un résultat qui va certainement influencer les prochaines architectures de processeurs.

Source: MIT, Papier scientifique

🔴 Pour ne manquer aucune actualité de 01net, suivez-nous sur Google Actualités et WhatsApp.